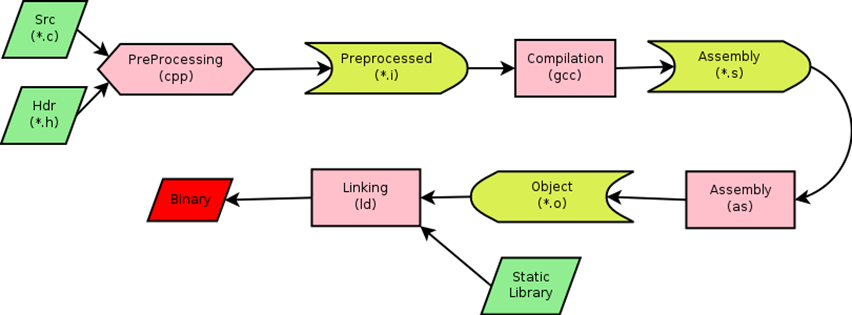

Compile 과정

1. 소스 파일 생성

2. 전처리기 (CPP, C Pre Processor)

Compile 전에 작동하여 #include, #define, 주석 제거 등을 담당

3. 컴파일러 (CC, C Compiler)

전처리기를 거친 소스 파일을 assembly어 파일로 변환

4. 어셈블러 (AS, ASsembler)

Assembly어 파일을 object 파일로 변환

5. 링커 (LD, Linker Directive) & 재배치 (Relocation)

Object 파일들을 묶어 하나의 실행 파일을 생성

Object 파일을 실제 주기억 장소에 맞추어 재배치 (상대주소를 절대주소로 변경)

컴파일 과정을 그림으로 보면 다음과 같다

Compile

cc hello.c

실행 파일은 기본적으로 a.out으로 출력 (권한은 755)

c hello.c –o hello.out

실행 파일은 hello.out으로 출력 (권한은 755)

Linux 계열에선 cc 대신 gcc를 이용해도 됨

사용법은 동일

cc hello.c –O(옵션)

-O0 ~ -O3 : 최적화 수준 설정

-Ofast : 실행 속도 위주로 최적화

cc hello.c –c

컴파일만 진행 (실행 파일을 만들지 않음)

결과물(목적 코드, 모듈)은 hello.o 파일로 출력

cc hello.c –S

어셈블리 코드로 생성

결과물은 hello.s 파일로 출력

Option

-c : compile only (linking 안함)

-g : debug

-help : help

-Ipathname : 헤더파일의 경로 지정

-llibrary : lib 추가

-Ldirectory : lib 경로 지정

-w :경고 무시

-static :static linking(default : dynamic)

ex) gcc –I/usr/local/cuda/include

–L/usr/local/cuda/lib64

–o main main.c

–lOpenCL

Files

a.out : default output file by compile

file.a : archive file

file.c : C source file

file.c |.cc|.cpp : C++ source file

file.i : 전처리 후 C source file

file.o : object file

file.s : assembler source file

Example

$gcc --help

$gcc hello.c

$gcc –o hello hello.c

$gcc –c hello1.c hello2.c

$gcc –o hello hello.c hello1.o hello2.o libtest.a

$gcc –g hello.c

$gcc –I../home/in –L../home/lib hello.c –ltest

$gcc –static hello.c

Makefile

Unix 계열에서 많이 사용하는 빌드 자동화 도구이다.

매니페스트 파일을 이용하여 과정을 자동화하며, Manifest, 특정한 목적 및 절차를 표현하는 명세서이다

비슷한 역할을 하는 툴에는 CMake, Java : Ant, IDE : Visual Studio, Eclipse, … 등이 있다.

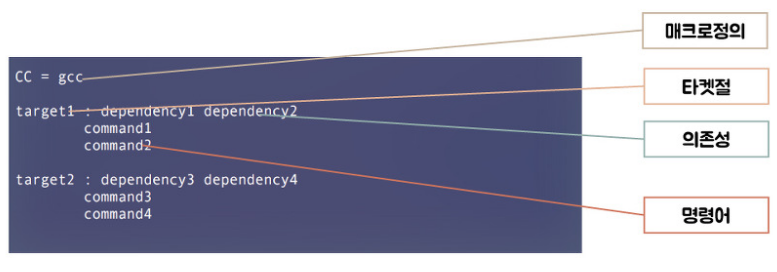

Makefile의 구조

목적파일(Target) : 명령어가 수행되어 나온 결과를 저장할 파일

의존성(Dependency) : 목적파일을 만들기 위해 필요한 재료

명령어(Command) : 실행되어야 할 명령어들

매크로 (Macro) : 코드를 단순화시키기 위한 방법

Makefile lines

dependency line

target : [prerequisites]

command line

“tab” [@] command

macro definition

name = string

include statement

include filenames

comment

# 주석

Makefile 이용하기

Makefile 작성

vi Makefile

make (목표 이름) –f (매니페스트 파일)

목표 이름 : 자동화할 목표를 지정

생략 시 최초에 서술된 목표로 지정

매니페스트 파일 : 목표가 명세 된 파일을 지정

생략 시 ‘Makefile’로 지정 (GNU Make)

디렉터리 지정 (GNU Make 전용) : -C (디렉터리)

예) make all –C hello

시뮬레이션(touch만 실행) : -t

새로 make를 실행한 것처럼 처리 (재컴파일 X)

ex) make 이후 main.c를 변경한 후 make –t 를 실행하면,

touch main.o diary_exe 를 수행

Makefile 실행

make

Makefile 개선하기

매크로를 사용하여 중복되는 파일 이름을 특정 단어로 치환

C언어에서 #define을 하는 것과 비슷한 원리

매크로 작성 규칙

매크로를 참조할 때는 소괄호나 중괄호로 둘러싸 앞에 ‘$’를 붙임

탭으로 시작해서는 안되며 ,:,=,#,”” 등은 매크로 이름에 사용불가

매크로는 반드시 치환될 위치보다 먼저 정의되어야 함

make의 매크로 사용은 유닉스 변수 사용과 동일

정의 : VAR = arguments (공백으로 구분)

사용 : $(VAR)

매크로 사용으로 컴파일 옵션 지정도 가능

make에서 사용하는, 미리 정의된 매크로 확인

make –p

'개발 > UNIX' 카테고리의 다른 글

| UNIX - 파일 및 디렉터리 조작하기 (0) | 2021.10.15 |

|---|---|

| UNIX - 파일 조작하기 (0) | 2021.10.14 |

| UNIX - main function, process, fork, exec (0) | 2021.10.09 |

| UNIX - current directory, sync / fsync, device files (0) | 2021.10.08 |

| UNIX - directory, directory library (0) | 2021.10.07 |